Altera FPGA的Avalon MM总线接口规范介绍

本文参考了Altera文档:1. Avalon接口规范简介

Avalon总线是一种片上总线,协议相对简单。它主要用于连接片上处理器和外设,形成片上可编程系统(SOPC)。 Avalon 接口可轻松连接英特尔FPGA 中的各种组件,从而简化系统设计。 Avalon 接口通常用于高速数据流传输、读写寄存器和存储器、控制片外设备等。此外,您还可以使用Avalon 接口定制组件,以增强设计的互操作性。

Avalon有以下七个接口:

Avalon Clock Interface,Avalon时钟接口——驱动或接收时钟信号的接口。

Avalon Reset Interface,Avalon复位接口——驱动或接收复位信号的接口。

Avalon Memory Mapped Interface(Avalon-MM),Avalon Memory Mapped Interface——基于地址的读/写接口,是主从连接的典型接口。

Avalon Streaming Interface (Avalon-ST),Avalon Streaming接口——支持单向数据流的接口,包括多数据流、数据包和DSP数据的传输。

Avalon Conduit Interface, Avalon Conduit Interface——适用于不适合任何其他Avalon 类型的单个/多个信号。使用此接口将信号导出到顶层SOPC系统,以便它可以连接到设计的其他模块。

Avalon Tri-State Conduit Interface (Avalon-TC),Avalon tri-state Conduit 接口——与片外设备的接口。多个外设可以通过信号复用来共享引脚,从而减少FPGA 引脚数和PCB 走线数。

Avalon Interrupt Interface,Avalon 中断接口- 允许组件向其他组件发送事件信号的接口。

一个组件可以包含多个不同类型的接口,或者多个相同类型的接口。

Avalon 接口通过属性描述其行为。每个接口类型的规范定义了该接口的所有属性和默认值。例如,Avalon-ST接口的maxChannel属性指定了该接口支持的通道数,Avalon Clock接口的clockRate属性描述了时钟信号的频率。

每个Avalon接口定义了一系列信号及其行为,并且大多数信号是可选的,允许组件设计者更灵活地选择他们需要的信号类型。例如,Avalon-MM 接口包括用于支持突发传输的组件的可选beginbursttransfer 和burstcount 信号。 Avalon-ST 接口包含支持数据包的接口的可选startofpacket 和endofpacket 信号。

每个接口都有描述单一类型传输的定时信息。

注:本实验仅使用Avalon时钟接口、Avalon复位接口、Avalon内存映射接口和Avalon Conduit接口。下面重点介绍这四个接口。其他接口请参考Intel FPGA Avalon接口规范文档。

阿瓦隆时钟接口

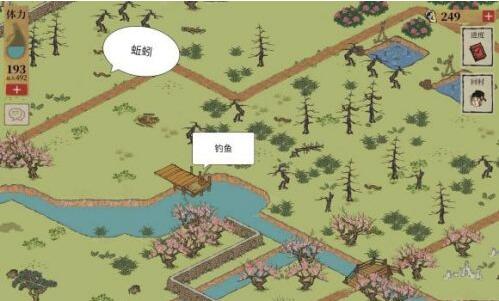

Avalon 时钟接口定义了组件使用的时钟。组件可以具有时钟输入、时钟输出或两者都有。例如,锁相环(PLL)是一个包含时钟输入和时钟输出的组件,如图所示。

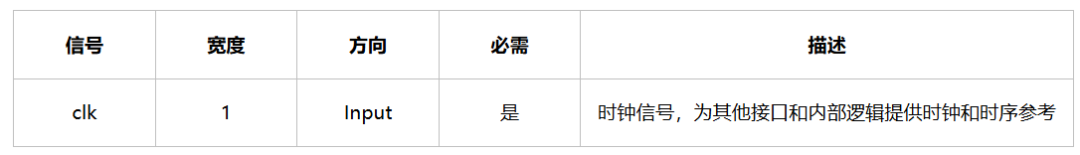

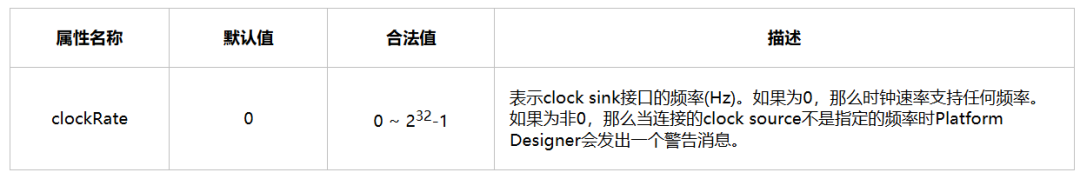

Clock Sink信号时钟接收器为其他接口和内部逻辑提供时钟和时序参考。时钟宿的属性包括clockRate,用于指示时钟宿接口的频率(Hz)。默认值为0。

表1 时钟接收信号

表2 时钟接收器属性

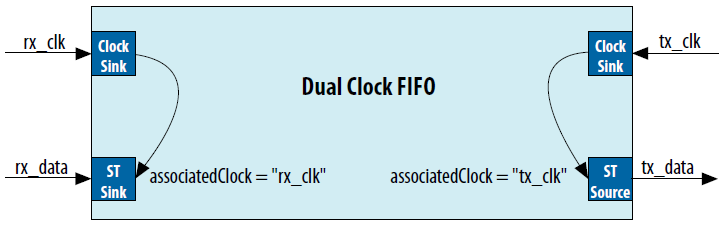

所有同步接口都有一个AssociatedClock 属性,用于指定组件上的哪个时钟源用作接口的同步参考,如图所示。

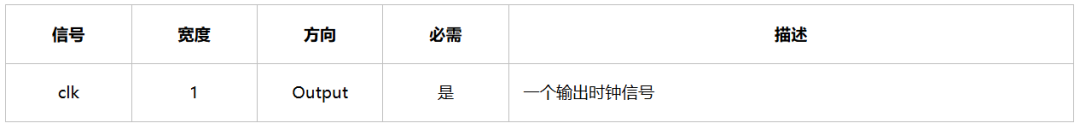

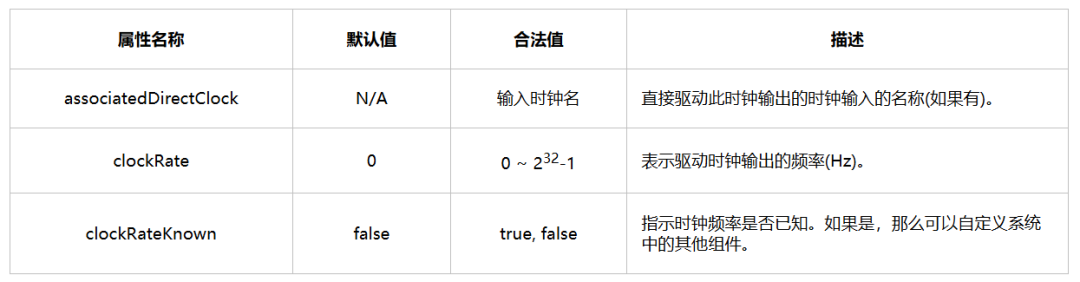

Clock Source信号时钟源接口输出来自组件的时钟信号。时钟源具有三个属性。 AssociatedDirectClock表示直接驱动时钟的时钟名称,clockRate表示时钟输出的频率,clockRateKnown表示时钟频率是否已知。

表3 时钟源信号

表4 时钟源属性

Avalon复位接口

与Avalon时钟接口类似,Avalon复位接口也分为Reset Sink和Reset Source。

Reset Sink复位接收器包含两个信号,reset/reset_n和reset_req。 reset_req 是一个可选信号。 Reset Sink有两个属性,associatedClock表示与接口同步的时钟,synchronous-Edges表示复位需要的同步类型,NONE表示不需要同步,DEASSERT表示复位是异步的,取消复位是同步的,BOTH表示复位和取消复位都是同步的。

所有同步接口都有一个AssociatedReset 属性,用于指定哪个复位信号复位接口逻辑。

表5 复位接收器信号

表6 复位接收器属性

重置源

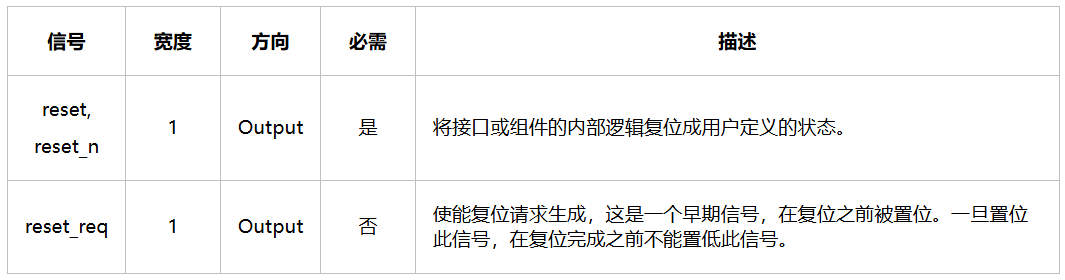

复位源还包含两个信号,reset/reset_n和reset_req。 reset_req 是一个可选信号。复位源有四个属性。 AssociatedClock表示与接口同步的时钟; AssociatedDirectReset 表示重置输入的名称。该复位输入通过一对一的链路直接驱动该复位源; AssociatedResetSinks用于指定复位输入,以便复位源复位; synchronous-Edges表示复位需要同步类型,NONE表示不需要同步,DEASSERT表示复位是异步的,取消复位是同步的,BOTH表示复位和取消复位都是同步的。

表7 复位源信号

表8 复位接收器属性

Avalon内存映射接口

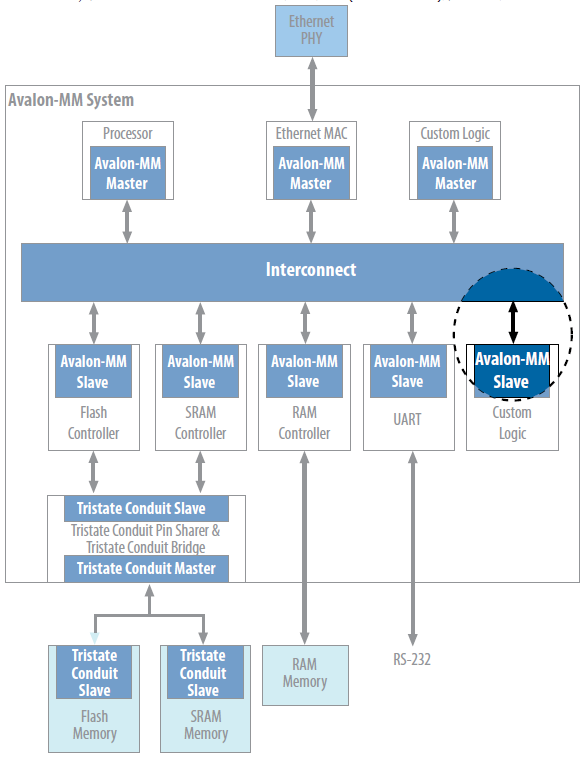

Avalon内存映射接口主要用于实现Master-Slave组件的读写接口。微处理器、存储器、UART、DMA 和定时器(Timer) 是包含Avalon 存储器映射接口的常用组件。 Avalon-MM 接口范围从简单到复杂。例如,SRAM 接口具有固定周期的读写传输,并具有简单的Avalon-MM 接口。能够进行突发传输的流水线接口包括更复杂的Avalon-MM 接口。这里我们只介绍简单的Avalon-MM接口。对于更复杂的流水线接口,请参考Intel FPGA的Avalon接口规范文档。

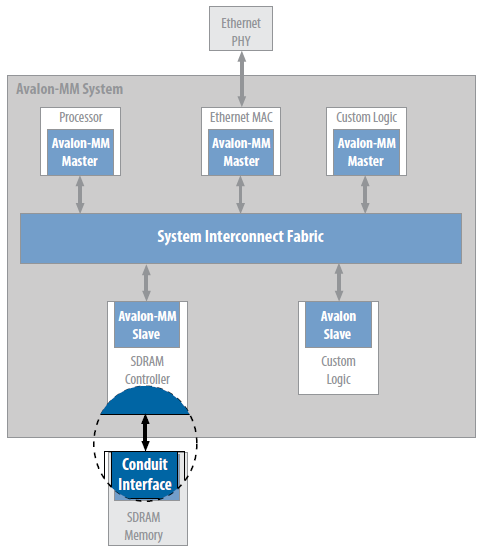

下图是一个典型的系统。图中突出显示并圈出的是Avalon-MM从接口和互连架构之间的连接。

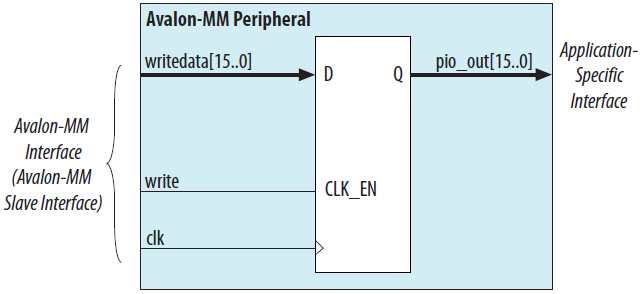

下图显示16位通用I/O外设仅响应写请求。该组件仅包含写传输所需的从机信号。

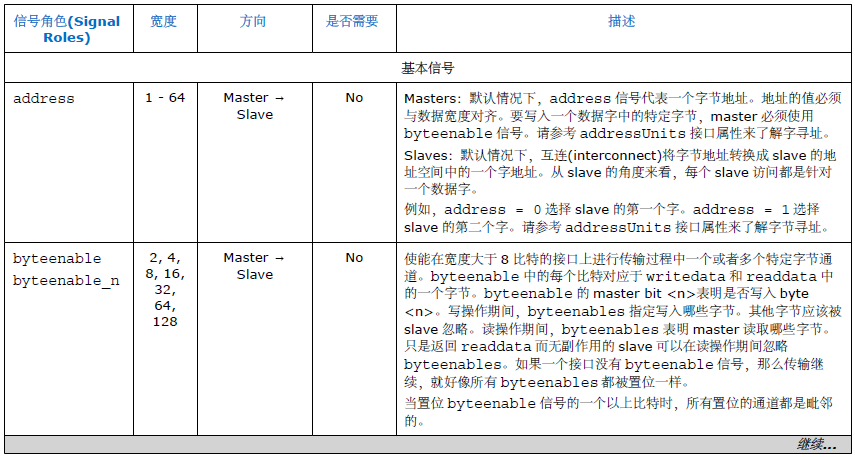

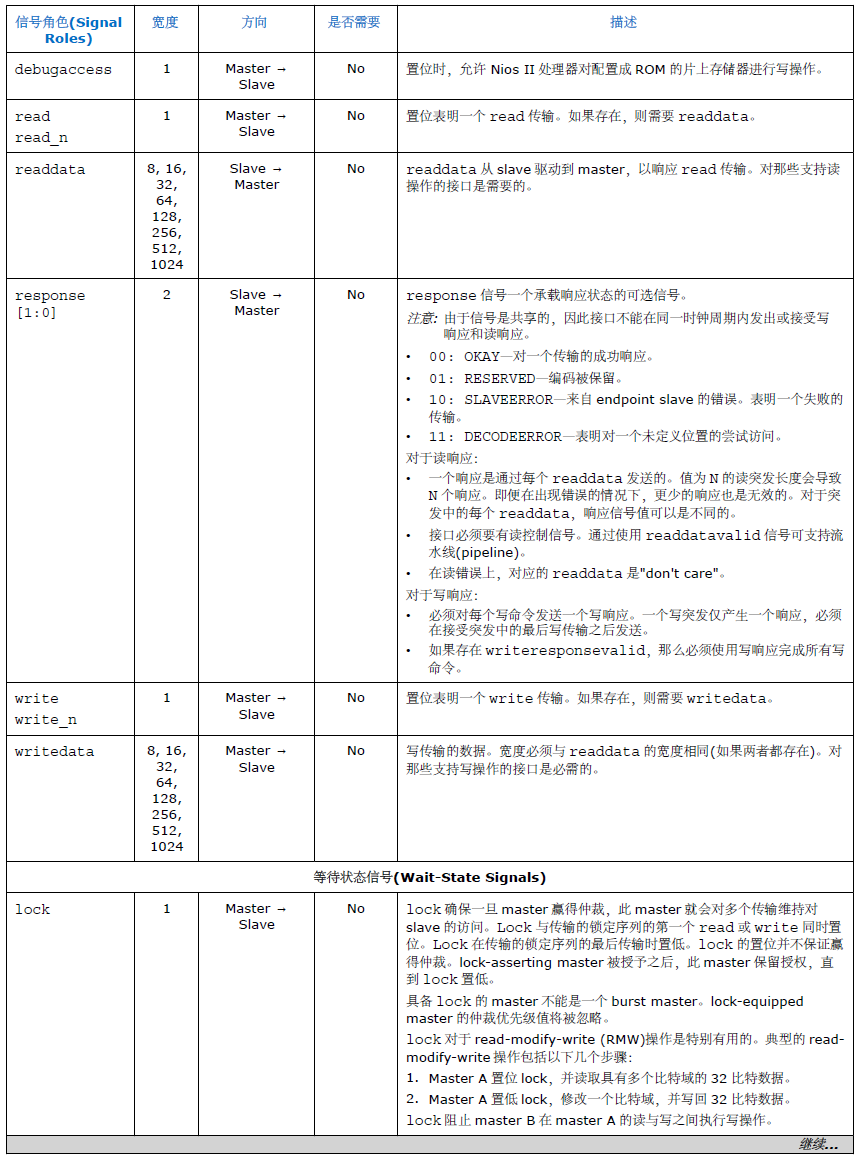

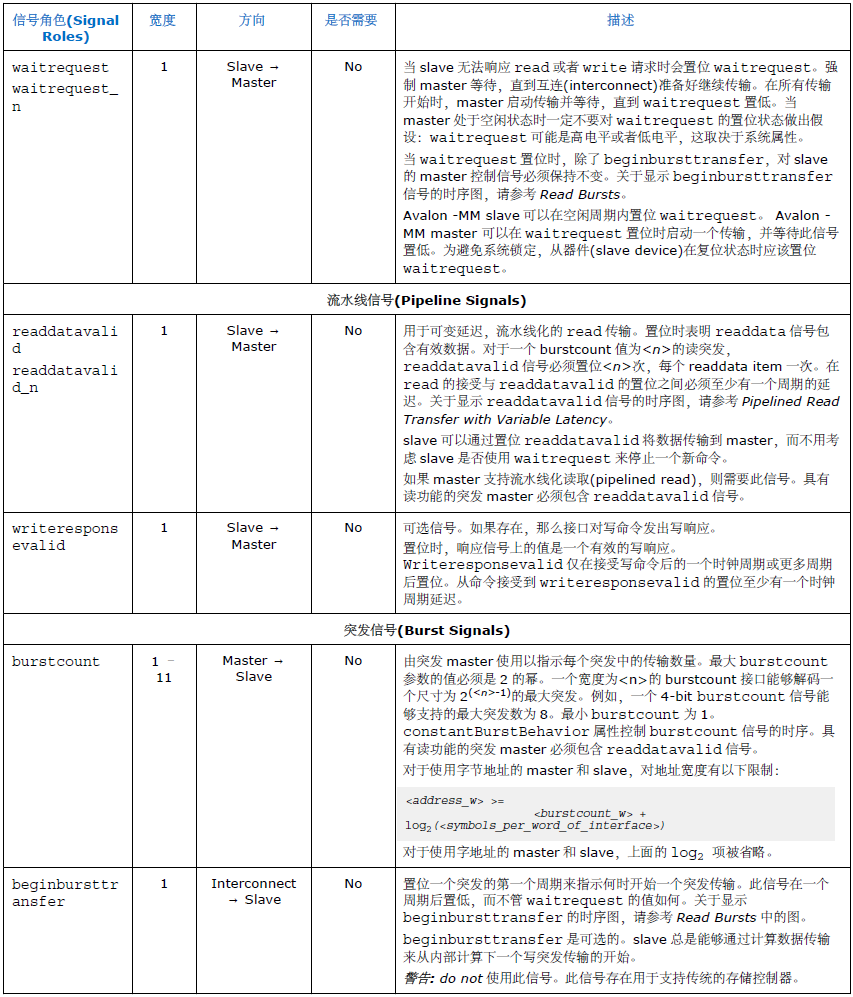

Avalon存储器映射接口信号及属性Avalon 接口规范文档的表9 列出了Avalon-MM 接口的信号。注:Avalon 规范不要求所有信号都存在于Avalon-MM 接口中。也就是说,当一个接口是Avalon-MM接口时,它只包含某些需要的信号。例如,对于只支持读操作(只读)的接口,它至少可以包含readdata信号;对于只支持写操作(write-only)的接口,它至少可以包含writedata和wrtie信号。

表9 Avalon-MM 接口信号

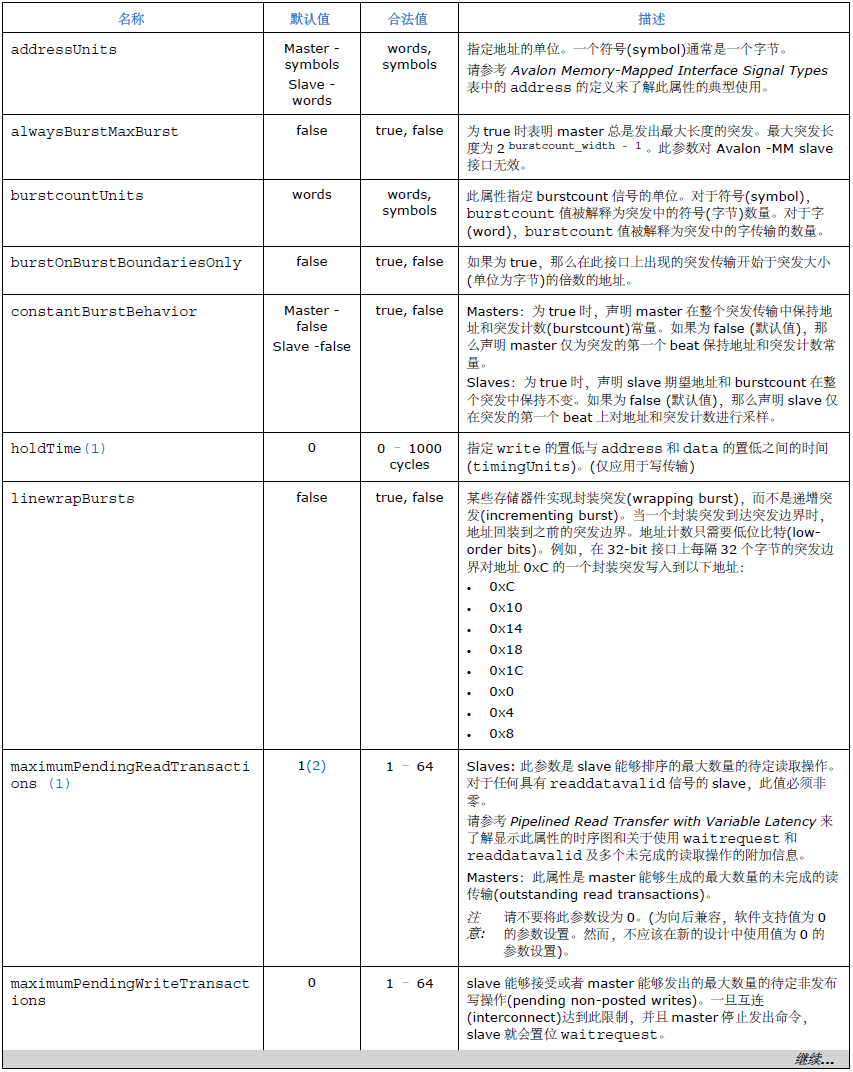

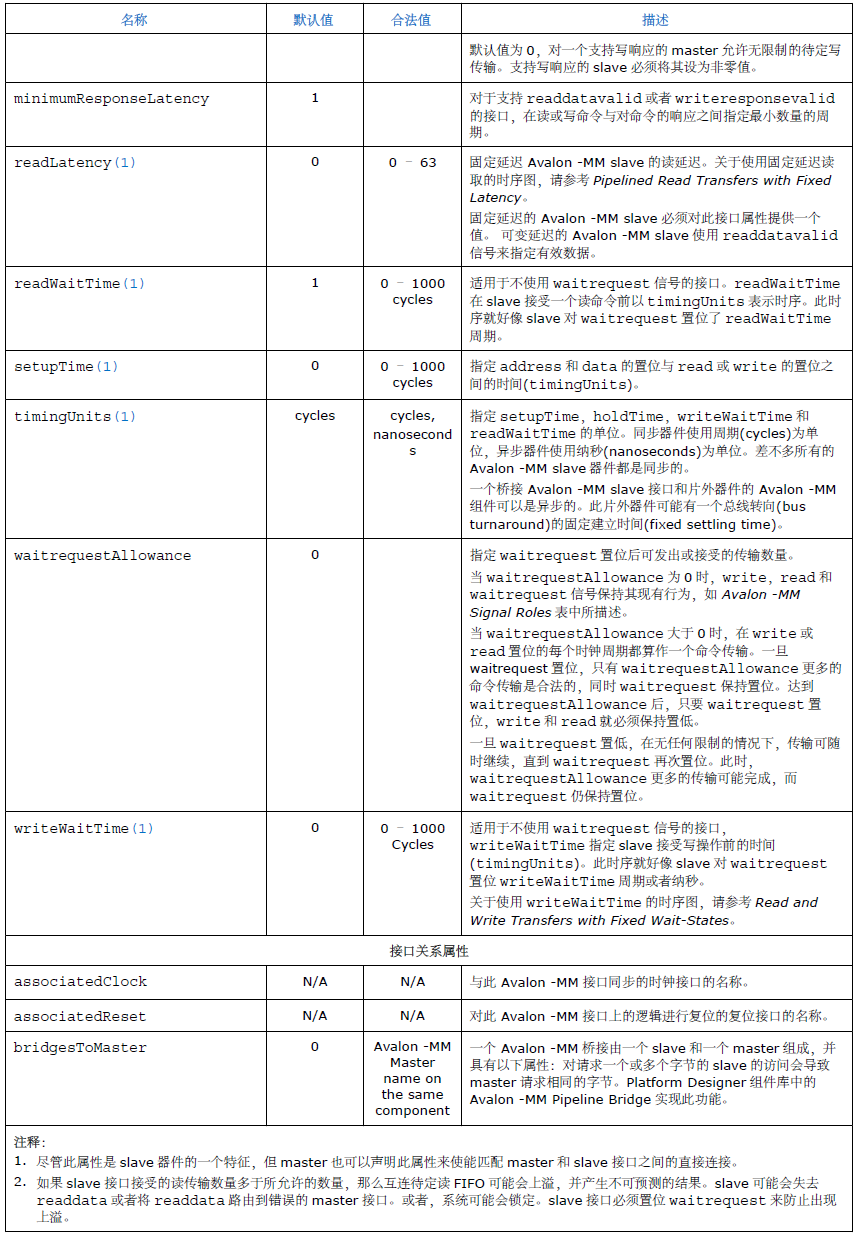

表10 列出了Avalon-MM 接口信号的属性。

表10 Avalon-MM 接口信号属性

Avalon-MM典型的读传输和写传输在介绍Avalon-MM的典型读写传输之前,我们先介绍两个基本概念:

传输- 传输是读取或写入一个字或一个或多个数据符号。传输发生在Avalon-MM 接口和互连之间。该传输需要一个或多个时钟周期才能完成。主设备和从设备都是传输的一部分。 Avalon-MM 主设备发起传输,Avalon-MM 从设备响应。

主从对——指一次传输中涉及的主接口和从接口。在传输期间,主接口控制和数据信号穿过互连结构并与从接口交互。

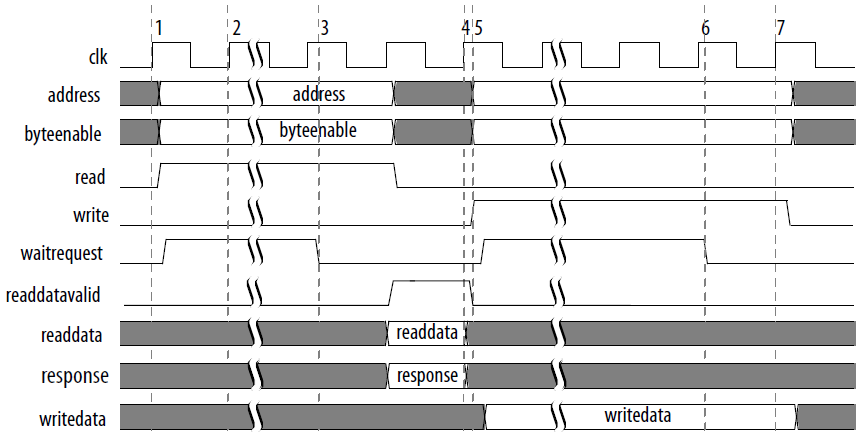

下面是一个用于读写传输的典型Avalon-MM 接口的示例。该接口包含waitrequest 信号。通过将waitrequest(高电平有效)信号设置为高电平,从机可以暂停互连。

通常,从机在时钟上升沿之后接收地址、字节码、读或写和writedata信号,并在时钟上升沿之前将waitrequest设置为高以暂停传输。当从机拉高waitrequest信号时,数据传输被延迟,地址线和其他控制信号保持不变。在从机拉低waitrequest 后的第一个时钟上升沿,读写传输完成。

从机可以无限期地拉起waitrequest信号,但在设计时,必须保证从机接口不会无限期地拉起waitrequest信号,以免出现从机没有响应而主机一直等待的现象。下图展示了使用waitrequest的读传输和写传输。

我们来分析一下上图中各个数字标记时刻Avalon-MM总线上的操作:

clk上升沿后,address、byteenable、read信号置位;从机将waitrequest 拉高以暂停数据传输。

在clk的上升沿,waitrequest被master采样;因为waitrequest有效,所以此时处于等待状态,address、read、byteenable保持不变。

从机在clk上升沿后将waitrequest设置为低电平,然后将readdata和response设置为有效。

在clk的上升沿,master检测到waitrequest被拉低,捕获readdata和response,读数据传输完成。

clk上升沿后,address、writedata、byteenable和write信号被置位;从机将waitrequest 拉高并暂停数据传输。

从机在clk 上升沿后将waitrequest 设置为低电平。

在clk的上升沿,slave捕获writedata,写数据传输完成。

地址对齐互连仅支持地址对齐访问。主设备只能发送为其数据位宽度的倍数的地址。 Master可以通过拉低byteenable_n的某些位来写入一些数据。例如,向地址2写入2字节数据时,byteenable_n=4’b1100。

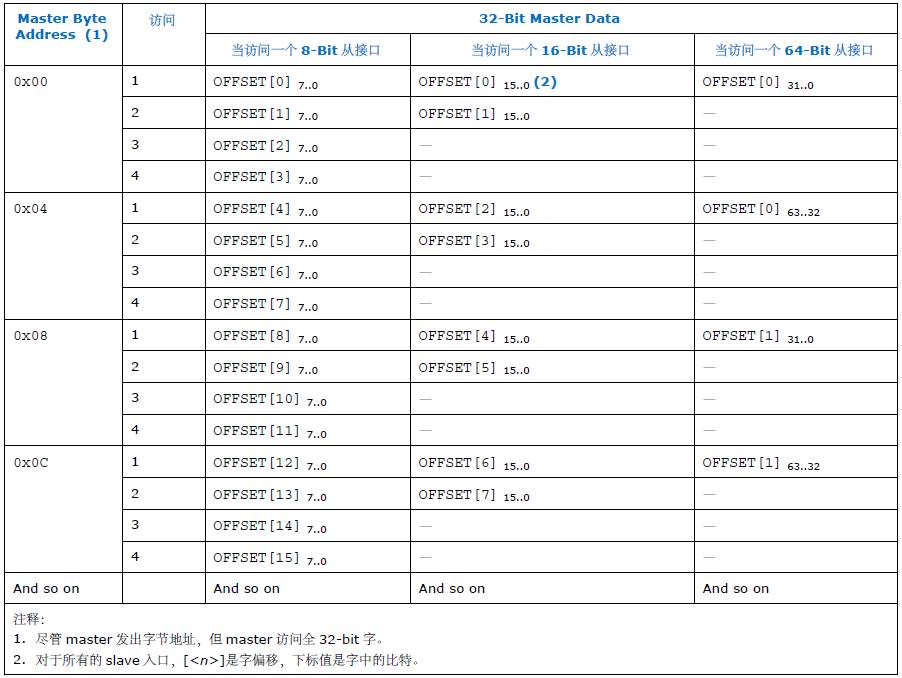

Avalon-MM寻址动态地址对齐(动态总线大小)管理不同数据宽度的主从对传输期间的数据。从机数据在主机地址空间中作为连续字节对齐。

如果主设备的数据宽度大于从设备的数据宽度,则主设备地址空间中的字将被映射到从设备地址空间中的多个位置。例如,当32位主机读取16位从机时,它将在从机端执行两次读传输。这两次读传输的地址是连续的。

如果主设备的数据宽度小于从设备的数据宽度,互连将管理从设备的各个字节通道。当主机从从机读取数据时,互连仅将相应字节通道的数据传输给主机。当主机向从机写入数据时,互连将自动断言相应字节通道的byteenables信号。

Slave 的数据宽度必须为8、16、32、64、128、256、512 或1024 位。下表列出了32位主机按字访问不同位宽的从机数据时如何与主机对齐。 OFFSET[N] 表示从地址空间字的偏移量。

表11 动态地址对齐的Master-Slave地址映射

AvalonConduit接口

Avalon Conduit 接口是不适合任何其他Avalon 类型的单个/多个信号的集合。使用此接口将信号导出到顶层SOPC系统,以便它可以连接到设计的其他模块。一个Avalon Conduit 接口可以包括输入、输出和双向信号,并且一个模块/组件可以有多个Avalon Conduit 接口。

Conduit接口通常用于驱动片外设备信号,如SDRAM的地址、数据和控制信号线,如下图所示。

Avalon管道接口的信号可以是任意的,并且该接口的信号没有任何属性。

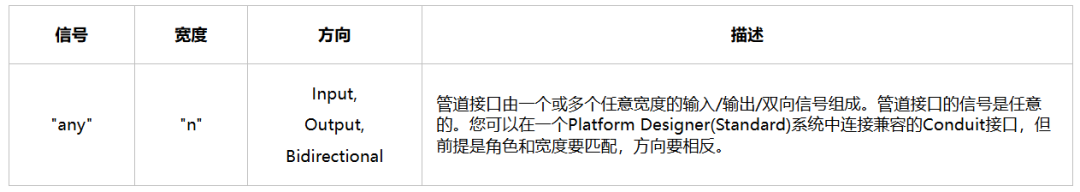

表12 导管接口信号