使用MATLAB和Simulink进行信号完整性分析

信号完整性是维持高速数字信号质量的过程。信号完整性是电信号从源传输到目的地时质量的关键衡量标准。在高速数字和模拟电子设备中,确保信号的预期形状、时序和功率得到维持,可确保数据传输的可靠和准确。

反射、噪声、电磁干扰(EMI) 和其他问题会严重降低信号质量。信号完整性的丧失可能导致一系列问题,包括间歇性故障、数据错误、系统故障,以及最终代价高昂的重新设计和财务损失。从复杂的印刷电路板(PCB) 设计到先进的通信系统,强大的信号完整性是可靠性能的基石。

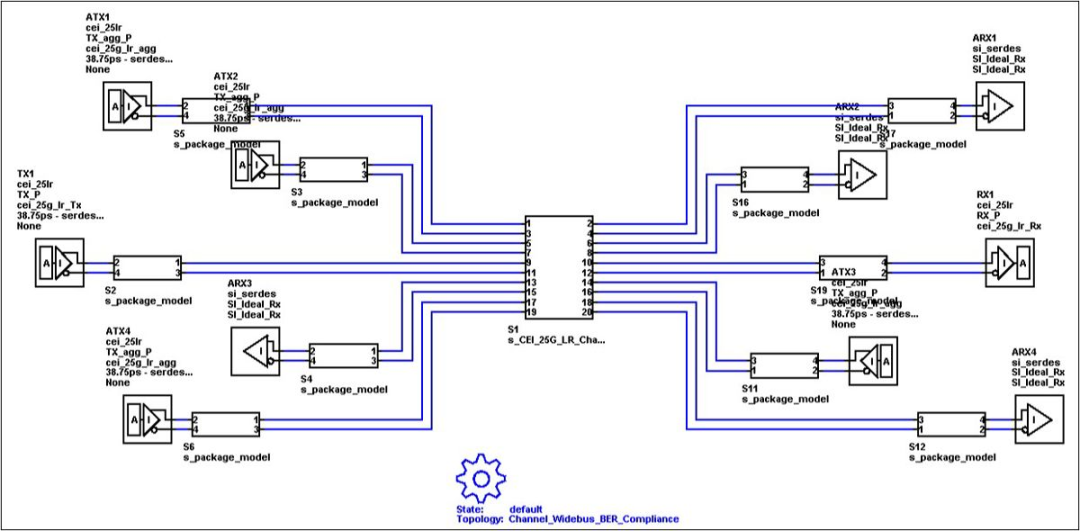

系统设计中信号完整性的角色高速设计中信号完整性的布局前分析实现良好信号完整性的关键步骤是预布局分析。此类分析通常在设计阶段进行,以识别潜在问题并帮助您做出明智的决策,以优化设计以实现信号完整性。

使用Signal Integrity Toolbox 中的串行链路设计器构建OIF CEI 25G-LR 预布局原理图。 (点击“阅读原文”即可获取文档链接)

通过执行布局前分析,您可以在设计周期的早期识别并解决潜在的信号完整性问题,从而降低以后昂贵的设计修订和修改的风险。此分析还可以帮助您优化设计以实现信号完整性,使其更加稳健并符合行业标准。

实际应用预布局PCB 信号完整性分析对于高速、高可靠性通信至关重要的行业和应用尤其重要,例如:

高吞吐量服务器依赖于通过背板和互连进行干净信号传输的数据中心

汽车电子,其中高级驾驶辅助系统(ADAS) 和信息娱乐系统需要强大的高速通信

DDR、LPDDR 和GDDR 等高速内存接口,其时序裕度很紧张,即使很小的失真也会导致数据损坏

通过将信号完整性仿真集成到早期设计阶段,您可以确保您的系统从一开始就满足性能目标和监管标准。

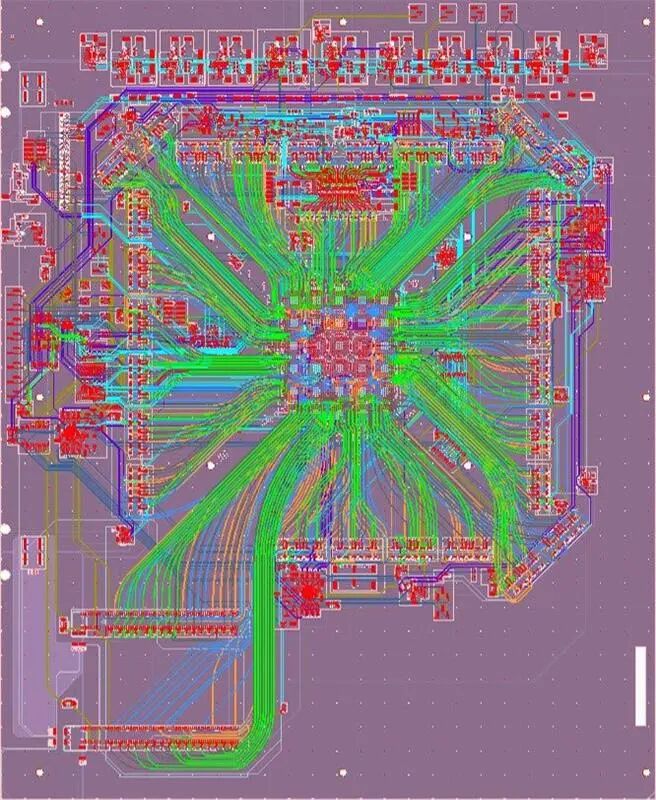

用于确保 PCB 信号完整性的布局后验证布局后验证涉及审查设计的物理实现,包括实际的PCB 布局和布线,目的是确保设计满足预期的信号完整性性能要求。此过程需要使用信号完整性仿真和分析工具(例如Signal Integrity Toolbox)来仿真最终设计的电气行为并识别任何潜在问题。

Signal Integrity Toolbox 提供的信号完整性查看器中显示的印刷电路板。 (点击“阅读原文”即可获取文档链接)

在布局后验证期间,您可以执行仿真来计算时序、电压电平和信号完整性指标(例如抖动、眼图高度/宽度和误码率(BER)),以验证设计的性能并确保其符合行业标准。

一旦发现任何信号完整性问题,您可以修改布局、布线或选定的组件并重新运行仿真,直到设计满足预期的性能要求。在某些情况下,布局后验证可能会揭示布局前分析中未发现的问题。为此,您必须进行必要的更改以满足设计要求。

实际应用布局后验证对于性能和合规性至关重要的行业至关重要,例如:

高速串行链路必须满足严格的信号完整性标准的电信基础设施

消费电子产品,紧凑的PCB 布局增加了干扰和信号衰减的风险

极端条件下的可靠性至关重要的航空航天和国防系统

通过将布局后信号完整性仿真集成到验证过程中,您可以确保您的高速数字设计稳健、合规且可投入生产。

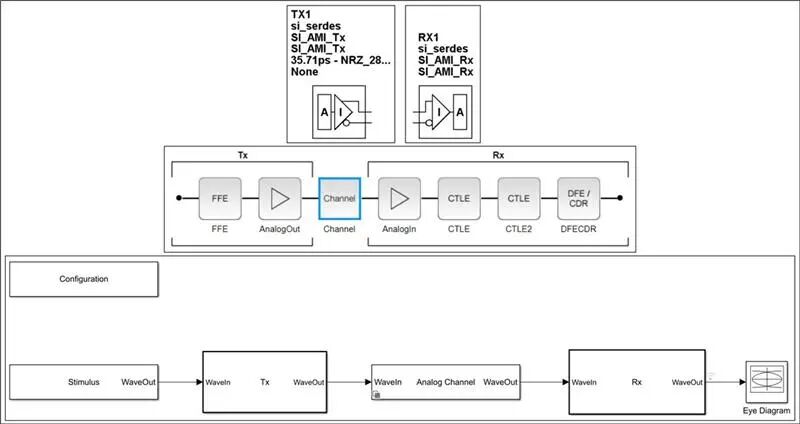

高速信号完整性的均衡和信道建模IBIS-AMI(I/O 缓冲区信息规范- 算法建模接口)是用于高速通道布局前分析和布局后验证的建模标准。 IBIS-AMI 将信号路径内组件的电气特性结合起来,形成完整的通道模型,使您能够更准确、更高效地模拟复杂的高速数字系统。

Signal Integrity Toolbox(上)、SerDes Designer(中)和Simulink(下)中显示的SerDes 系统的IBIS-AMI 模型。 (点击“阅读原文”即可获取文档链接)

在布局前和布局后分析中使用IBIS-AMI 模型可以帮助您优化设计时间、降低设计错误的风险并提高高速数字系统的整体信号完整性性能。然而,创建准确可靠的IBIS-AMI 模型可能是一个复杂且耗时的过程,需要技术专业知识。您可以使用SerDes Toolbox 中的内置支持进行统计和时域仿真、IBIS-AMI 参数管理以及自动生成IBIS-AMI 兼容模型,从而使您能够专注于设计优化和验证。

实际应用均衡和通道建模对于高速数据必须通过复杂或有损介质传输的系统至关重要,例如:

数据中心互连,长距离的PCB 走线和电缆可能会导致严重的信号丢失

DDR、LPDDR 和GDDR 等高速存储器接口,其时序裕度要求严格,需要精确的信号调节

汽车以太网和信息娱乐系统,其中均衡可确保双绞线电缆上的可靠通信

通过将信号完整性仿真与均衡和通道建模相集成,您可以设计出在具有挑战性的物理约束下满足性能目标的系统。

信号完整性分析中的合规性和标准验证在电子行业,确保符合行业标准是信号完整性分析的关键部分。随着数据传输速率的提高和协议变得更加复杂,验证设计是否符合行业规范对于数据传输可靠性和产品认证至关重要。

使用MATLAB 和Simulink,您可以针对各种高速接口标准执行自动合规性检查,包括:

PCI Express (PCIe)

USB 3.x 和USB4

光互联网论坛(OIF) 和IEEE 802.3 以太网

DDR/LPDDR/GDDR 内存接口

汽车以太网和MIPI 标准

这些工具使您能够模拟真实的操作条件,生成眼图,并评估抖动、噪声容限和误码率,以确保您的设计满足所需的阈值。这种级别的信号完整性仿真可帮助您在硬件测试之前识别并解决问题,从而降低代价高昂的重新设计或合规性失败的风险。

实际应用合规性验证在强制执行互操作性和认证的行业中尤为重要,例如:

消费电子产品,设备在上市前必须通过USB 合规性测试

以太网和MIPI 接口必须满足严格的EMI 和时序标准的汽车系统

企业网络和存储,其中PCIe 和高速内存接口必须在繁重的数据负载下提供一致的性能

通过将合规性验证集成到高速数字设计工作流程中,您可以确保您的产品不仅功能齐全,而且合规并准备好进行全球部署。

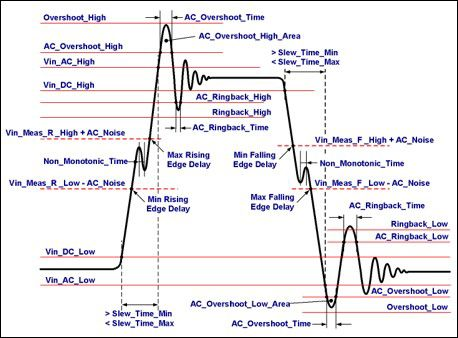

信号完整性分析度量和可视化在高速数字设计中,信号在传输过程中必须保持完整,以实现良好的信号完整性性能。常用的指标和可视化包括:

电压裕度:电压裕度测量信号幅度和信号噪声裕度之间的差异。电压裕度应足够高,以确保信号能够在接收器处可靠地解调。

时序分析:该指标涉及计算信号的上升和下降时间、传播延迟和抖动。您可以使用时序分析来评估设计的时序预算并确保信号在所需的时序窗口内转换。

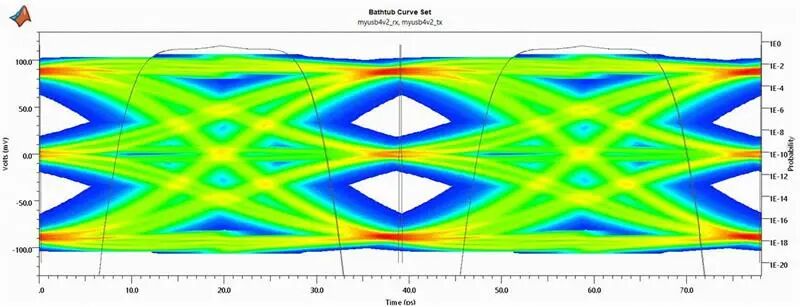

抖动:抖动是信号时序随时间的变化。抖动可能有多种原因,包括信号失真、串扰、电源噪声和衰减。您可以使用抖动直方图和眼图来识别和分析高速数字系统中的抖动。

眼图:眼图用于分析信号性能随时间的变化并识别潜在的信号完整性问题。它们涉及绘制信号随时间变化的幅度,通常以直方图的形式。这种可视化方法可以全面了解信号的行为,包括抖动、噪声和时序问题。

误码率:BER 是用于计算数据流中错误位数的指标。 BER 值越高,信号完整性越差。您可以使用BER 来量化设计的信号完整性性能,然后优化设计以降低BER。

衰减:衰减是衡量信号随距离或时间损失的指标。如果衰减较高,可能会导致信号失真和信号失败。您可以使用衰减测量来评估信号的性能并设计传输线和电路以最大限度地减少衰减。

串扰:串扰是指一个信号的电场对相邻信号造成的噪声干扰。您可以使用串扰测量来评估通道之间的干扰水平、计算串扰耦合系数并确定降低串扰水平的设计方法。

时域反射计(TDR):TDR 通过将信号的输出与从传输线末端反射的输入信号进行比较来测量传输线的阻抗。此方法有助于识别传输线上的阻抗变化和信号完整性问题。

通道工作裕度(COM):COM 量化了设计中信号眼图与最坏情况损伤影响之间的裕度。 COM 可帮助您评估设计中的信号完整性性能并确定需要改进的领域。

波形示例显示在Signal Integrity Toolbox 的并行链路设计器中测量的阈值和参数。 (点击“阅读原文”即可获取文档链接)

PAM3 眼图是使用Signal Integrity Toolbox 创建的,并显示在Signal Integrity Viewer 中。 (点击“阅读原文”即可获取文档链接)

使用 MATLAB 和 Simulink 进行信号完整性分析为了主动应对这些挑战,您可以使用MATLAB 和Simulink 进行信号完整性分析。通过对整个系统进行建模和仿真,您可以在构建物理原型之前检测眼图闭合、抖动、误码率过高以及其他潜在问题。这种虚拟测试使您能够设计和验证均衡方法、优化高速链路并确保整体信号质量,从而在开发周期中节省大量时间和资源。

通过使用MATLAB 和Simulink 产品进行信号完整性分析,您可以执行:

高速设计中的预布局分析:在PCB 布局开始之前,使用仿真和建模来识别和解决潜在的信号完整性问题。

布局后验证:使用布局后PCB 信号完整性验证来验证真实信号行为并检测布局引起的问题。

均衡和通道建模:设计和模拟均衡策略,以减轻信号失真并保持有损通道上的数据完整性。

合规性和标准验证:通过自动化合规性测试和仿真,确保您的设计符合PCIe、USB 和DDR 等行业标准。

信号完整性工具箱、SerDes 工具箱、RF PCB 工具箱和混合信号模块组提供从系统布局前分析到布局后验证的功能,同时生成可视化结果,例如眼图、波形图、频谱图、眼图轮廓和时钟偏差预算分析。这些工具提供了一种全面的方法来防止数据通信系统或高速电子设备出现问题。