1 实验要求

在FPGA上生成1280x720@60分辨率的视频信号,并通过DE10-Nano的HDMI输出到显示屏。显示的内容是一个黑色方块,每10ms 移动一个像素。当正方形遇到边界时会反弹。屏幕背景为白色,屏幕边框为绿色。

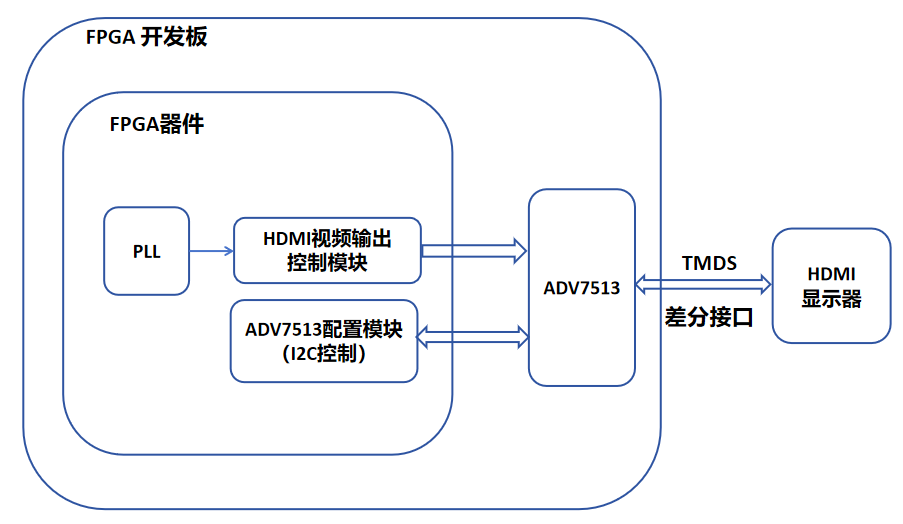

2 设计框图

根据实验需求分析,可以得出结论,如果想要控制ADV7513最终在HDMI显示器上显示图片,需要先配置ADV7513寄存器,并通过I2C总线进行配置。这部分的控制原理前面已经讲解过(参考文末往期阅读链接)。

如果要在HDMI 显示器上显示边框、正方形和白色背景,则需要设计满足DMT 时序的视频信号。

1280x720@60分辨率的像素时钟为74.25MHz,所以这里可以调用Altera的PLL IP来生成这个时钟(系统时钟为50MHz)。

整个系统的设计框图如下:

3 代码实现

(1)顶层代码

主要实例化了三个模块:PLL、HDMI显示和I2C控制。具体代码请参考项目。

(2)HDMI控制器模块

HDMI控制器模块用于生成1280x720分辨率的视频信号,并在屏幕上显示一个每10ms移动一次的黑色方块,背景为白色,屏幕边框为绿色。

1、首先是1280*720分辨率时序参数的设置。以下是行计时参数设置:

这些参数对应的时序如下图所示:

以下为现场计时参数设置:

这些参数对应的时序如下图所示:

2. 实现行计数器和场计数器来跟踪当前像素位置并生成像素的水平和垂直坐标:

3.根据水平和垂直计数器生成水平和垂直同步信号:

4、根据行场计数器生成像素点的横纵坐标:

5、hdmi_ctrl模块的时钟为74.25MHz(像素时钟对应1280*720@60),用一个计数器产生10ms的间隔:

6、当方块移动到边界时,改变移动方向:

根据代码绘制的方向变化框图如下:

7、根据方块的移动方向改变其纵横坐标:

8.给不同的区域涂上不同的颜色:

(3)I2C控制模块

I2C控制模块直接参考本文8.3章(内容完全一样)。

4 硬件准备

DE10-Nano开发板一套(含电源和USB线)

一台HDMI 显示器

HDMI线一根

5 软件安装1、进入Altera官网,选择Quartus Prime Lite 17.1版本:

2. 点击Individual Files找到Cyclone V器件包并下载:

3、继续找到Intel Quartus Software,下载QuartusLiteSetup压缩包和ModelSimSetup压缩包(后面会有仿真章节):

4. 下载所有文件后,双击QuartusLiteSetup-17.1.0.590-windows.exe 文件进行安装。安装过程中会默认安装Nios II IDE、ModelSim和Cyclone V器件包(这些内容如果没有勾选,可以自行查看)。建议安装过程中保留所有默认设置(自行选择安装路径除外)。软件安装结束时将提示安装USB Blaster II 驱动程序。 6 操作步骤1. 打开Quartus 软件,点击File——New Project Wizard.

2. 单击下一步:

3. 在下面的对话框中选择项目路径和项目名称:

4、继续点击下一步:

5、继续点击下一步:

6、然后在如下对话框中输入DE10-Nano(5CSEBA6U23I7)对应的FPGA器件:

7、点击Finish结束项目创建:

8.开始创建新的Top项目并单击File——New.

9. 选择Verilog HDL 文件并单击确定:

10.编译Verilog代码(代码可以参考本文提供的工程)并保存为HDMI_block_move.v文件:

11、用同样的方法新建一个.v文件,编译Verilog代码(代码可以参考本文提供的工程)并保存为hdmi_ctrl.v文件:

12. 将第8 章中提到的I2C 控制器中包含的三个.v 文件复制到当前项目路径:

13、将这三个文件添加到当前工程中,以便以后编译时调用这三个文件。具体方法是点击Project——Add/Remove Files in Project.然后点击File Name旁边的.浏览到三个文件的路径,选择这三个文件并点击Open按钮:

14.然后点击Apply和OK按钮结束添加项目文件:

15.接下来配置PLL IP,在IP Catalog中搜索pll,找到Altera PLL,然后点击它:

16. 在下面的对话框中,将pll的名称填写为pll,然后单击确定:

17.Reference ClockFrequency填写50,outclk0填写74.25,然后点击Finish结束pll配置:

18. pll模块生成后,会弹出如下对话框。单击“是”将其添加到当前项目:

19、此时FPGA电路设计基本完成。接下来是引脚分配。首先点击Start AnalysisSynthesis按钮对工程进行分析综合,这样在后续引脚分配时就可以出现信号端口了:

20. 接下来,参考DE10-Nano的用户手册文档或原理图文件来分配管脚。本项目的引脚分配如下:

21、引脚分配完成后,点击Start Compilation按钮,开始完整的编译工程:

22、工程完全编译后,会在HDMI_block_moveoutput_files路径下生成HDMI_block_move.sof文件。接下来,单击Programmer 按钮将此文件配置到FPGA 中:

23. 点击硬件设置(执行此操作之前,请记住使用HDMI 线连接HDMI 显示器和DE10-Nano,然后使用Mini USB 线连接PC 和DE10-Nano,然后为DE10-Nano 开发板插入5V 电源),选择DE-SoC [USB-1] 端口,然后点击关闭:

24. 单击“自动检测”,选择“5CSEBA6”,然后单击“确定”:

25. 如果出现以下窗口,请单击“是”:

26、此时系统中会出现两个设备,一个是SOCVHPS,另一个是5CSEBA6U23。右键单击5CSEBA6U23 并选择更改文件:

27. 浏览至HDMI_block_move.sof 路径并选择该文件,然后单击“打开”:

28. 单击以下复选框,然后单击Start 开始FPGA 文件配置:

29. 当Progress进度条显示100%(颜色变为绿色)时,表示FPGA配置完成:

7个实验现象

可以观察到HDMI显示屏上有一个绿色边框,中间背景为白色,屏幕上有一个黑色小方块在移动。

HDMI_block_move项目下载链接: https://pan.baidu.com/s/1LwQjqLpmZMl5IkvTgzo-3w

提取码: tera

标题:使用DE10-Nano的HDMI方块移动案例的整体实现

链接:https://yqqlyw.com/news/sypc/70576.html

版权:文章转载自网络,如有侵权,请联系删除!