1 I2C简介

I2C(Inter-Integrated Circuit)是飞利浦半导体(现为恩智浦半导体)于20 世纪80 年代初开发的一种同步、串行、半双工总线型通信协议。主要用于芯片间近距离(同一印刷电路板(PCB)上的集成电路(IC)之间)和低速(注:标准模式100K、快速模式400K、高速模式3.4M)的通信。

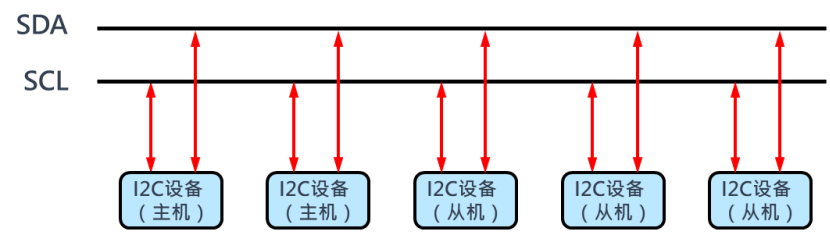

I2C总线有两根信号线,一根数据线SDA用于发送和接收数据,一根时钟线SCL用于同步双方时钟。 I2C 总线是多主总线。连接到I2C总线的设备分为主设备和从设备。主站有权发起和结束通信,而从站只能由主站调用。连接到I2C 总线的每个设备都有一个唯一的地址(7 位)。主机通过I2C 设备的地址选择从机。

2 I2C三态门电路

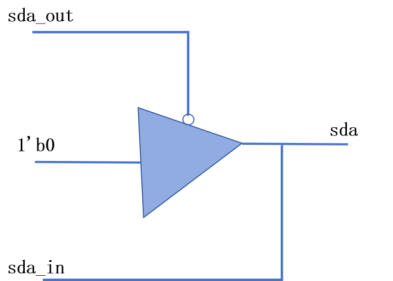

当信息在两个方向(方向为inout)传输时,需要三态门电路。 FPGA内部三态门结构:

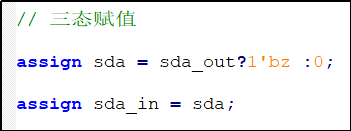

当sda_out为1时,sda被设置为高阻状态(1'bz),即此时sda受外部器件(或上拉电阻)控制。当sda_out为0时,sda被驱动为0。本设计符合I2C协议的开漏输出特性:I2C设备只能将数据线拉低(输出0)或释放(输出高阻,通过上拉电阻拉高)。因此,这种三态设置可以实现I2C 数据线的双向通信:可以输出数据(拉低),也可以输入数据(释放总线并读取)。具体Verilog实现如下:

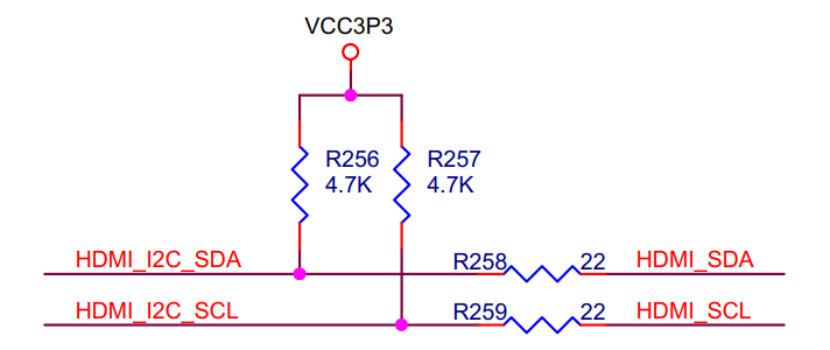

因此,FPGA与外设之间必须有上拉电阻。以下是DE10-Nano的相关电路图:

3 I2C协议的起始和结束信号

启动条件是当SCLK(时钟引脚)保持高电平时,SDIN(数据引脚)由高电平变为低电平,然后开始地址和数据传输;停止条件定义为当SCLK为高电平时,SDIN由低到高跳变:

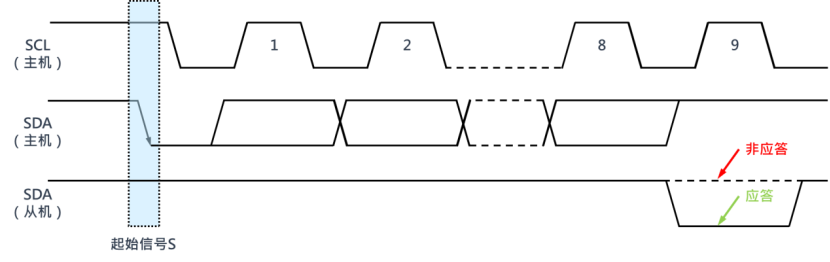

I2C协议的4字节传输和响应

在I2C 总线上通信时,每个字节为8 位长。传输数据时,先传输最高位,然后传输低位。发送器发送一个字节的数据后,接收器必须发送一个1 位的响应位(响应:低电平‘0’;无响应:没有收到数据或者接收器不想响应,所以保持高电平‘1’)来响应发送器,即一帧有9 个比特。

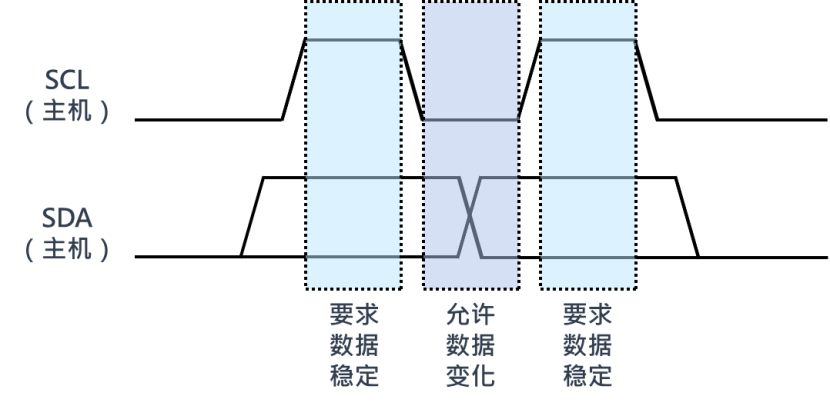

5 I2C协议的同步信号

I2C总线传输数据时:

当时钟线SCL为低电平时,发送器发送1位数据到数据线上,期间允许数据线上的信号改变;

当时钟线SCL为高电平时,接收器从数据线上读取1位数据。在此期间,数据线上的信号不允许发生变化,必须保持稳定。

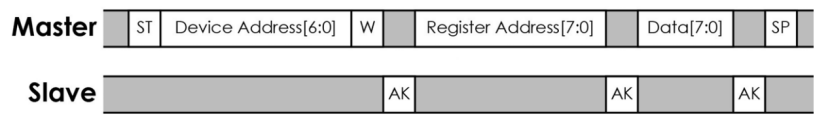

6 I2C协议的写操作

主机首先产生起始信号ST,然后主机发送要控制的设备地址Device Address[6:0],加上1位W/R读写位(设置为0)。从机收到主机发送的8位信号后,会回应ACK信号;然后发送寄存器地址[7:0](有些寄存器地址是16位,可以分两次发送)。从机收到主机发送的8位信号后,会回应ACK信号;然后发送8位数据Data[7:0]。从机收到主机发送的8位信号后,会回应一个ACK信号。传输完成后,主机会发出停止信号SP。然后就完成了将数据Data[7:0]写入Device Address[6:0]设备中的Register Address[7:0]寄存器:

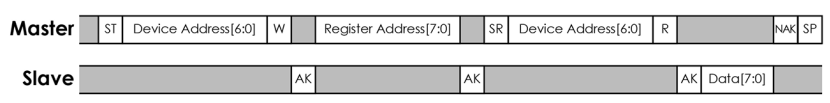

7 I2C协议的读操作

主机首先产生起始信号ST,然后主机发送要控制的设备地址Device Address[6:0],加上1位W/R读写位(设置为0)。从机收到主机发送的8位信号后,会回应ACK信号;然后发送寄存器地址Register Address[7:0]。从机收到主机发送的8位信号后,会回应ACK信号;然后主机重新发送启动信号SR(重启),然后主机发送要控制的设备地址DeviceAddress[6:0],加上1位W/R读写位(置1)。从机收到主机发送的8位信号后,会回应一个ACK信号。然后读取8位数据Data[7:0]。主机收到8位信号后,向从机发送NACK,通知从机主机不再需要更多数据。最后主机发出停止信号SP:

标题:基于FPGA的I2C通信协议设计

链接:https://yqqlyw.com/news/sypc/62339.html

版权:文章转载自网络,如有侵权,请联系删除!