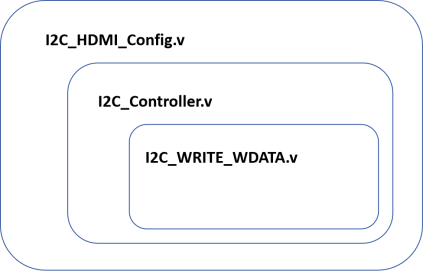

I2C_WRITE_WDATA.v 模块实现I2C 写入时序。 I2C_Controller(I2C控制器)实例化I2C_WRITE_WDATA.v模块,并为I2C数据线SDA添加三态缓冲电路。 I2C_HDMI_Config.v是顶层模块,实例化I2C_Controller模块,划分系统时钟,并控制寄存器的配置。

1 I2C写操作的Verilog实现

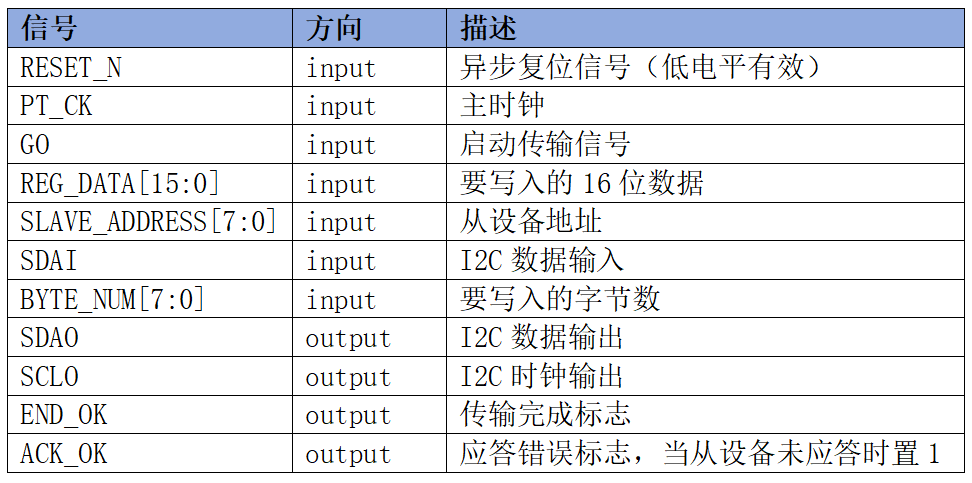

I2C_WRITE_WDATA.v是I2C写数据模块,用于通过I2C总线向从设备ADV7513写入数据。

模块接口定义如下:

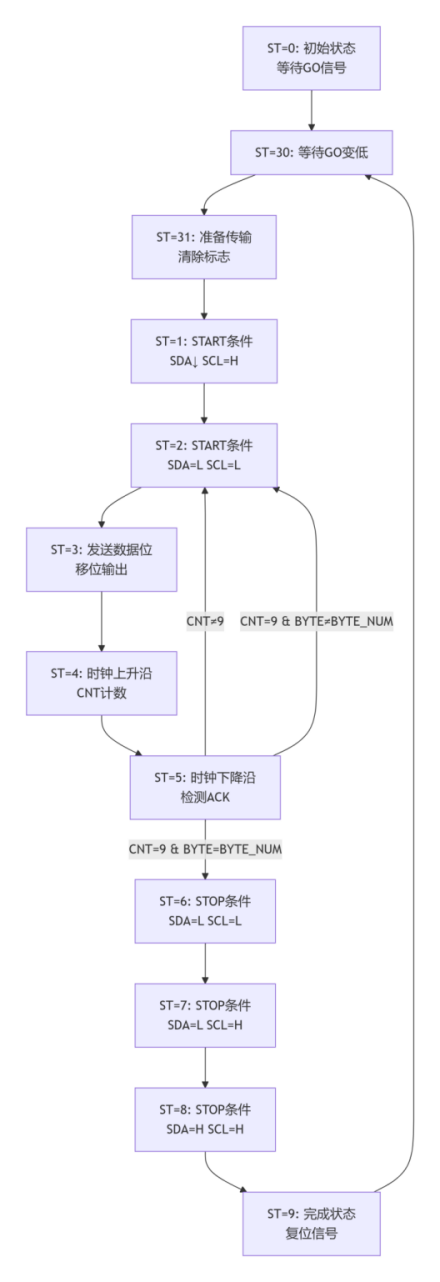

该模块实现了一个状态机,其功能是将多个字节的数据写入从设备。它根据I2C 协议生成启动条件、发送从机地址(包括读/写位)、发送数据字节并生成停止条件。同时,它也会检测从设备的响应信号,并在传输完成后给出结束信号。具体流程如下:

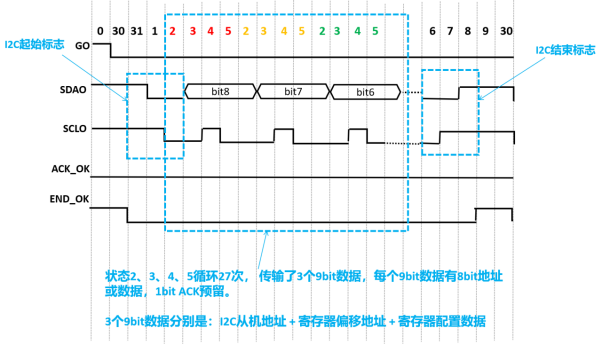

为了更好的理解这个状态机的控制逻辑,将I2C传输某个寄存器的过程波形绘制如下:

2 I2C三态门电路的Verilog实现

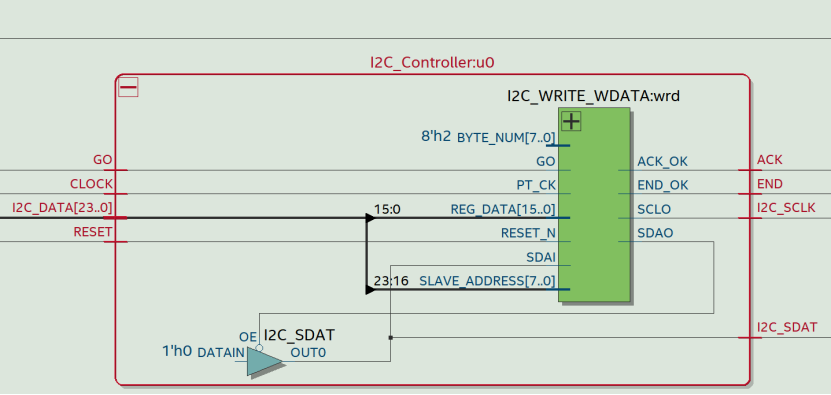

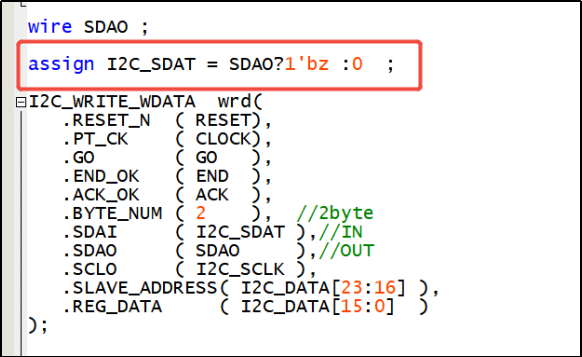

I2C_WRITE_WDATA.v 模块在I2C_Controller.v 中实例化:

该模块在I2C_WRITE_WDATA.v模块的SDAI和SDAO之间添加了一个三态门电路:

在I2C_WRITE_WDATA模块中,SDAO是输出信号,用于控制数据线的输出状态。当需要输出高电平时,将SDAO置1,使I2C_SDAT为高阻,并通过上拉电阻拉高;当需要输出低电平时,将SDAO设置为0,将I2C_SDAT拉低。同时,I2C_WRITE_WDATA模块还接收SDAI(即I2C_SDAT)作为输入,用于读取总线上的实际状态(例如检测ACK信号)。

3 I2C配置寄存器的Verilog设计

这是一个HDMI寄存器配置模块,使用查找表(LUT)来存储配置数据,然后通过I2C控制器(实现I2C协议)将配置一一写入到HDMI发送寄存器中。

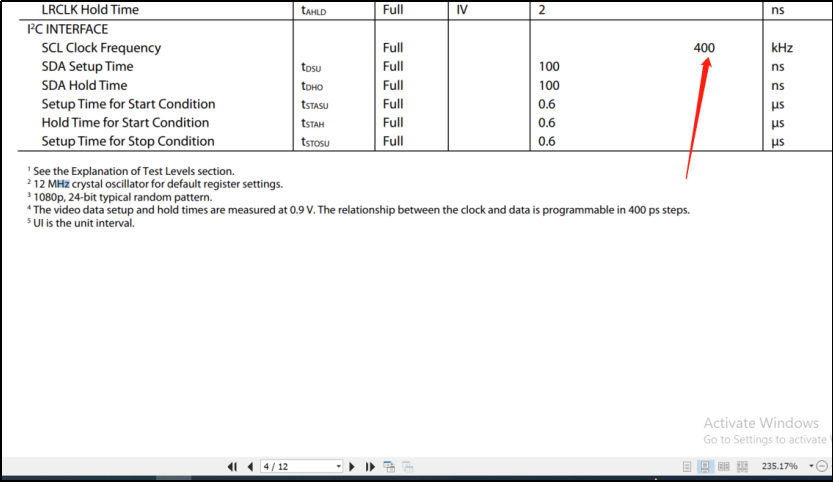

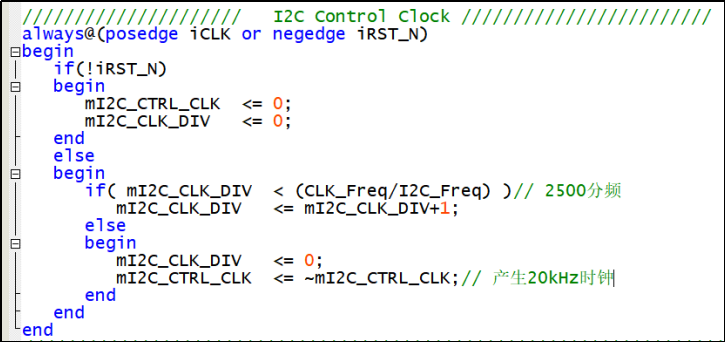

时钟分度

一般FPGA开发板板载系统时钟为50MHz,但I2C时钟不能太高。根据手册,最大不能超过400KHz,所以设计代码时需要进行分频。

Verilog代码将50MHz时钟划分为20KHz时钟:

配置寄存器

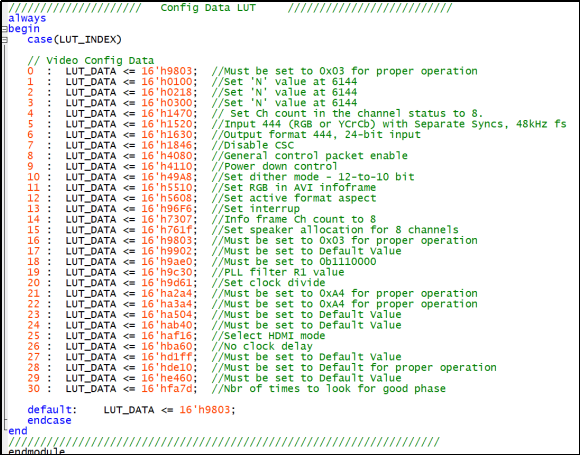

寄存器配置的值通过查找表(LUT)存储。代码中主要配置了31个寄存器。其他没有配置的则表示使用默认配置。关于ADV7513的寄存器查找,请参考2 ADV7513寄存器配置章节。

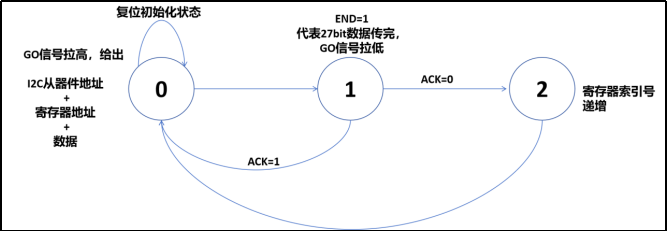

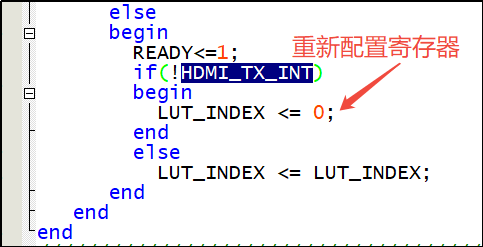

寄存器数据的配置由三态状态机控制:

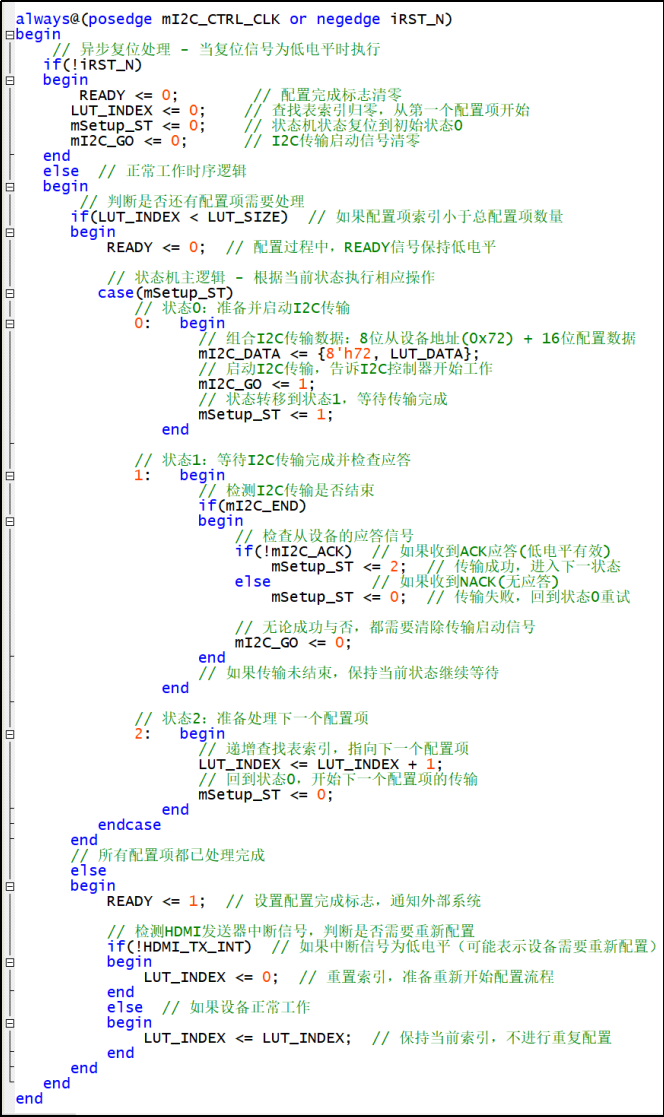

状态机完整代码如下:

该状态机保证了HDMI配置数据的可靠传输,具有完善的错误处理和重试机制,是HDMI初始化过程中的核心控制逻辑。

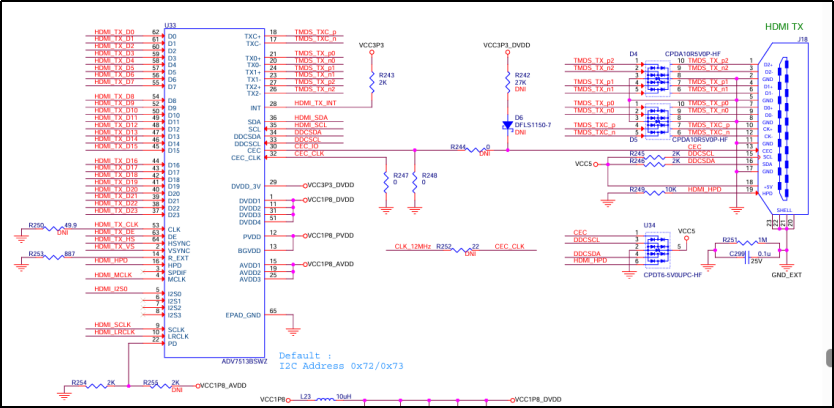

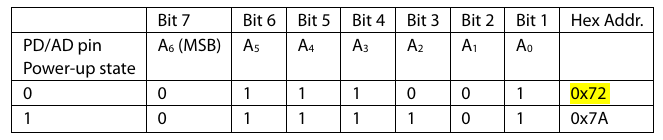

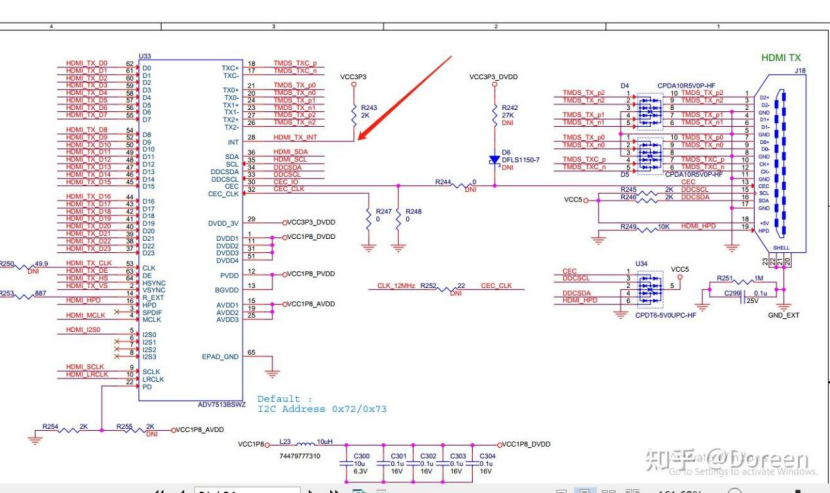

I2C设备地址

ADV7513的PD引脚连接2K电阻接地:

参考ADV7513_Hardware_User's_Guide_R0.pdf文档,我们可以看到其I2C读写地址为0x72/0x73:

HDMI_TX_INT信号

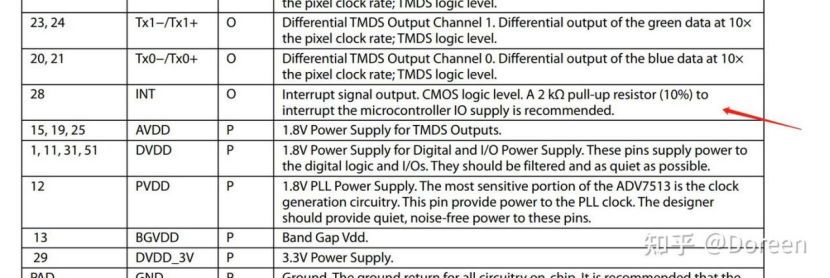

HDMI_TX_INT信号低电平有效。详细说明请参考ADV7513_Hardware_User's_Guide_R0.pdf第17页:

在DE10-Nano开发板电路中,

默认情况下,该引脚被拉高至3.3V。当中断事件发生时,软件控制该信号的电平变化。

I2C_HDMI_Config.v文件中设置,如果HDMI_TX_INT信号为低电平,则寄存器将被重新配置:

标题:基于FPGA的I2C控制模块设计

链接:https://yqqlyw.com/news/sypc/62338.html

版权:文章转载自网络,如有侵权,请联系删除!